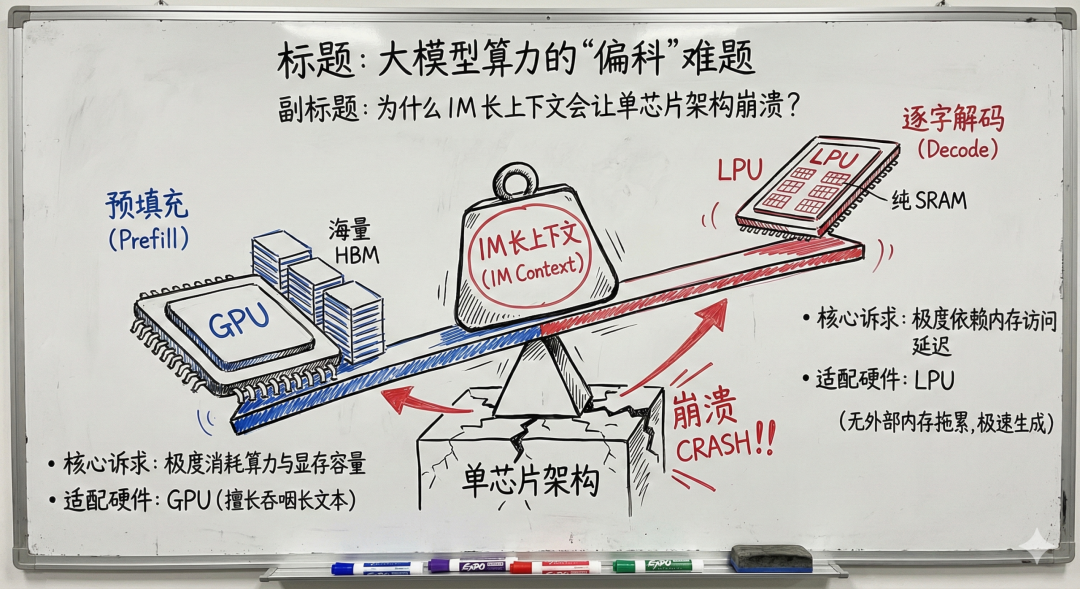

在处理 100K 甚至 1M 超长上下文时,AI 算力正面临严重的"偏科"挑战:

- 处理输入的预填充 (Prefill) 阶段,极度消耗庞大的浮点算力和显存容量。

- 生成输出的解码 (Decode) 阶段,却极度依赖极低的内存延迟。

目前没有任何单一架构能完美兼顾这两者。如何破局?答案指向了软硬协同的终极进化。

一、分离式架构 (PD Disaggregation):让合适的芯片做擅长的事

既然没有完美的单芯片,那就用架构来弥补。业界正转向一种跨硬件的异构协同模式:

- 用重型算力对抗重型计算:让拥有海量高带宽内存 (HBM) 的 GPU 阵列负责暴力吞咽长文本,生成数十 GB 的 KV Cache。

- 用极速缓存对抗生成延迟:让抛弃片外内存、采用纯 SRAM 的 Groq LPU 接管后续任务,以纳秒级的极低延迟完成逐字解码。

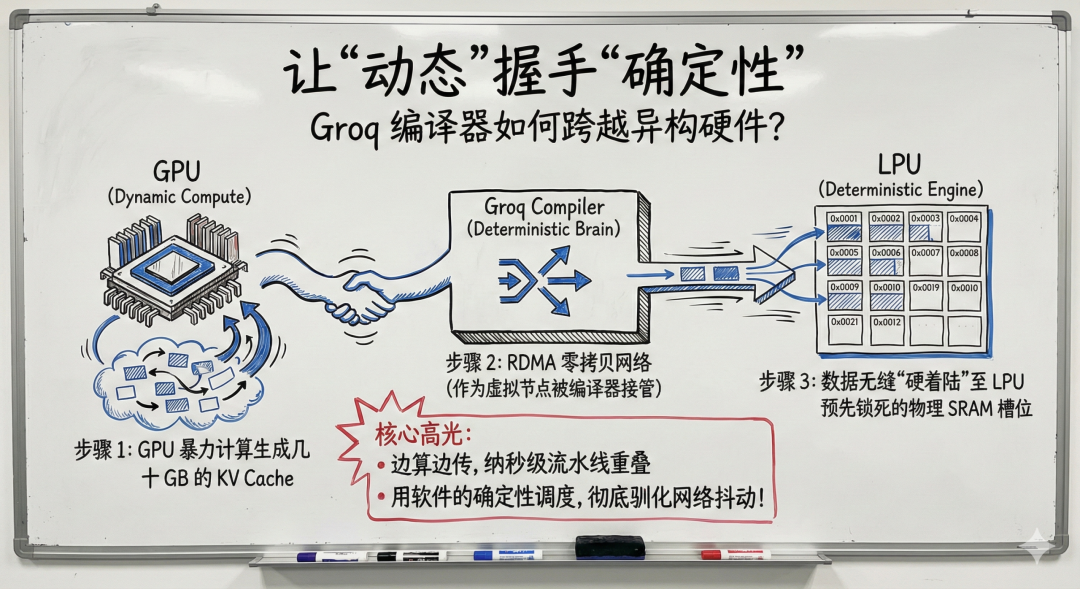

二、软件魔法:确定性编译器征服动态网络

GPU 与 LPU 的结合并非拉一根网线那么简单。GPU 的运算充满动态的随机性,而 LPU 需要绝对的周期精确 (Cycle-accurate),稍有不慎,涌入的数据就会撑爆 LPU 极小的 SRAM。

这里的关键在于编译器的"拓扑扩展"。Groq 的编译器将物理网卡视为一个带有已知延迟的虚拟节点,通过静态内存分配和 RDMA 零拷贝技术,让 GPU 端生成的数据直接穿透网络,"硬着陆"在 LPU 预先锁死的物理 SRAM 槽位中。边算边传,依靠纳秒级的流水线重叠和边缘 FIFO 队列,成功将外部不可控的网络抖动,驯化为内部极度可控的确定性数据流。

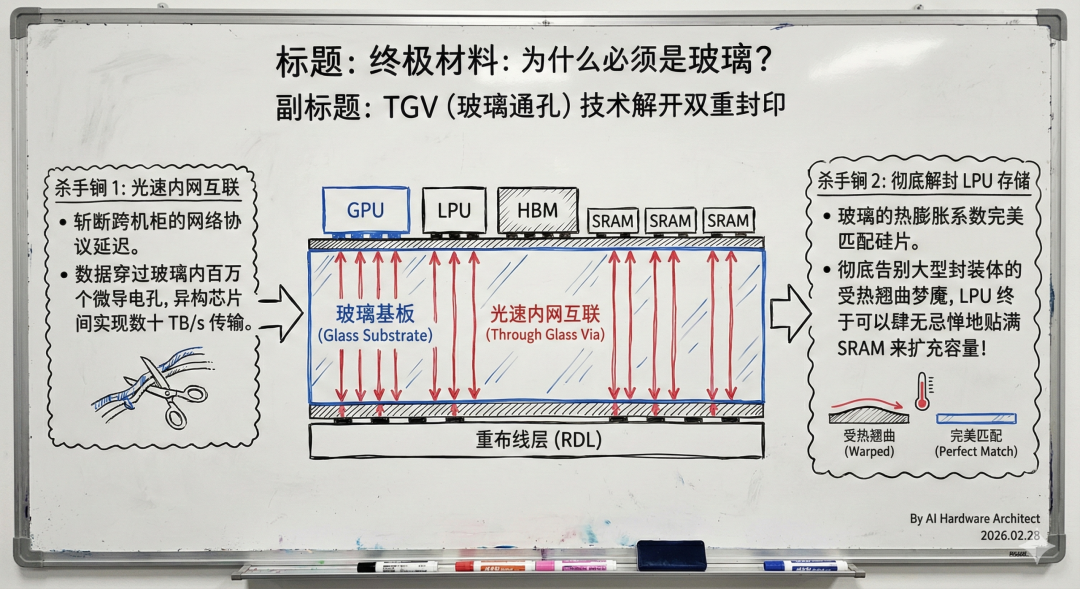

三、终极杀器:基于 TGV 的 CoPoS 面板级封装

如果说软件优化是极限微操,那么 TGV (玻璃通孔) 加持的 CoPoS 面板级封装,就是物理层面的降维打击。

跨越晶圆尺寸的极限

传统的硅基 CoWoS 封装受限于 12 英寸圆形晶圆的物理天花板。而 CoPoS 彻底摒弃了硅片,转而使用 500mm 以上的大尺寸矩形玻璃面板。这意味着,我们可以将重型计算的 GPU 芯粒、极速生成的 LPU 芯粒,以及海量的 HBM 和 SRAM,像拼图一样全部高密度封装在同一个超大模块内部。原本庞大的机柜级异构系统,被直接微缩成了一块超级基板。

光速互联与存储解封

玻璃基板绝佳的电介质特性配合内部数以百万计的 TGV 微孔,彻底消灭了跨设备传输的网络协议延迟。GPU 与 LPU 之间的数据转移带宽飙升至数十 TB/s。更重要的是,玻璃完美匹配了硅的热膨胀系数,让 LPU 终于可以在周围肆无忌惮地贴满 SRAM 存储芯粒来成倍扩充容量,彻底告别了大型封装体受热翘曲的梦魇。

总结

大模型推理硬件的尽头,远不止先进制程的无脑堆砌。依靠跨越异构架构的软件编译器大脑,配合玻璃基板与先进封装的物理骨架,一个在同一块面板上完美融合极致吞吐与极致延迟的"算力奇点"即将到来。